**\$22.8 million convertible bridge facility Update on memory market and STT's powerful ST-MRAM technology**

## Disclaimer

The following presentation, including any printed or electronic copy of these slides, the talks given by the presenters, the information communicated during any delivery of the presentation and any question and answer session and any document or material distributed at or in connection with the presentation (together, the "Presentation"), has been prepared by the Company. The information in the Presentation is not intended to form the basis of any contract. By attending (whether in person or by telephone) or reading the Presentation, you agree to the conditions set out below.

THIS PRESENTATION IS NOT A PROSPECTUS. The Presentation does not constitute or form part of any offer or invitation to sell or issue, or any solicitation of any offer to purchase or subscribe for, any shares or other securities of the Company, nor shall it (or any part of it), or the fact of its distribution, form the basis of, or be relied on in connection with or act as any inducement to enter into, any contract whatsoever relating to any securities.

The Presentation is provided for general information only and does not purport to contain all the information that may be required to evaluate the Company. The information in the Presentation is provided as at the date of the Presentation (unless stated otherwise) and is subject to updating, completion, revision and further verification. No reliance may be placed for any purpose whatsoever on the information or opinions contained or expressed in the Presentation or on the accuracy, completeness or fairness of such information and opinions. To the extent permitted by law or regulation, no undertaking, representation or warranty or other assurance, express or implied, is made or given by or on behalf of the Company, or any of its parent or subsidiary undertakings of any such parent undertakings or any of their respective directors, officers, partners, employees, agents, affiliates, representatives or advisors, or any other person, as to the accuracy, completeness or fairness of the information or opinions or opinions or opinions or opinions or for any loss, cost or damage suffered or incurred, however arising, directly or indirectly, from any use of, as a result of the reliance on, or otherwise in connection with, the Presentation. In addition, no duty of care or otherwise is owed by any such person to recipients of the Presentation or any other person in relation to the Presentation.

Nothing in the Presentation is, or should be relied on as, a promise or representation as to the future. The Presentation includes certain statements, estimates, opinions and projections provided by the Company in relation to strategies, plans, intentions, expectations, objectives and anticipated future performance of the Company and its subsidiaries. By their nature, such statements, estimates, opinions and projections involve risk and uncertainty since they are based on various assumptions made by the Company concerning anticipated results which may or may not prove to be correct and because they may relate to events and depend on circumstances that may or may not occur in the future and may be beyond the Company's ability to control or predict. No representations or warranties of any kind are made by any person as to the accuracy of such statements, estimates, opinions or projections, or that any of the events expressed or implied in any such statements, estimates or projections following the date of this Presentation. No statement in the Presentation is intended as a profit forecast or a profit estimate.

Certain industry and market data contained in this Presentation has come from third party sources. Third party industry publications, studies and surveys generally state that the data contained therein have been obtained from sources believed to be reliable, but that there is no guarantee of the accuracy or completeness of such data. While the Company believes that each of these publications, studies and surveys has been prepared by a reputable source, the Company has not independently verified the data contained therein. In addition, certain of the industry and market data contained in this Presentation comes from the Company's own internal research and estimates based on the knowledge and experience of the Company's management in the market in which the Company operates. While the Company believes that such research and estimates are reasonable and reliable, they, and their underlying methodology and assumptions, have not been verified by any independent source for accuracy or completeness and are subject to change without notice.

By accepting receipt of, attending any delivery of, or electronically accessing, the Presentation, you acknowledge and agree to be bound by the above limitations and conditions.

# **Allied Minds introduction**

- \$22.8 million convertible bridge facility, underwritten by Allied Minds with other investors expected to participate

- Bridge to Series B fund-raise planned for Q1 2018, expected to include new investors

- Extensive evaluation confirmed market opportunity, strength of STT's technical differentiation, team

- External diligence by senior industry experts, potential customers, partners

- STT's technologies have potential to enable MRAM to replace SRAM and DRAM (>\$20bn market opportunity)

- Technologies, fab, patent protection and team position STT for success

- Under new CEO, STT on clear path to commercialization

- Product roadmap, milestones to deliver commercial-grade MRAM

- Potential customer, partner engagement underway

- New additions to team, team aligned to deliver results

- Bridge provides run-way to deliver on early milestones and secure strategic partners for Series B fund-raise

## Summary

- MRAM has potential to replace embedded SRAM and key DRAM segments

- DRAM is \$20Bn market; limits of DRAM challenged, especially for enterprise and mobile

- MRAM has potential to disrupt SRAM and DRAM markets

- STT technology has potential to meet requirements for SRAM and DRAM replacement

- STT's differentiated technology and capabilities expected to enable meaningful performance advantages for its own and third party structures, in time for emerging market

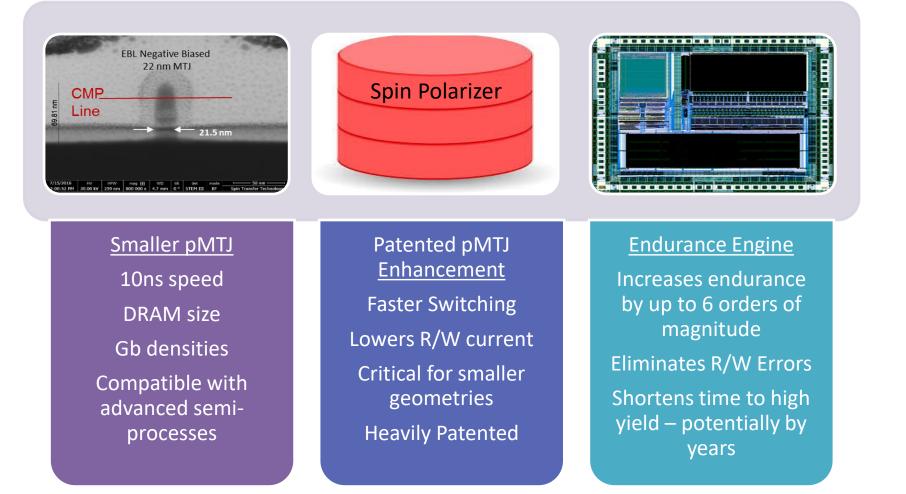

- Three core elements:

- Smaller, faster pMTJ structures

- Patented/Pending Spin Polarizer

- Patented/Pending Endurance Engine

- Fast turn, world-class Fabrication plant

- Multi-disciplined, synergistic engineering team

# Holy Grail: \$20B DRAM Market

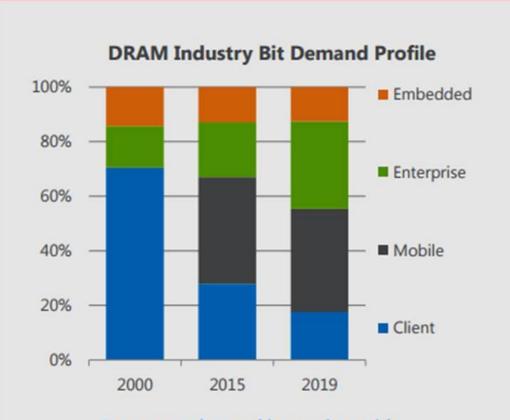

Aggregate demand increasing, with continued shift to mobile and enterprise

- Enterprise and Mobile represent greatest opportunity – estimated \$20bn market

- Fastest growing segments

- Power, persistence and cost are most important

- DRAM commands a price premium

- DRAM reaching the physical limits of its capabilities; difficult to shrink further

- MRAM has the potential to meet the needs of these markets

- Lower power and lower cost

# DRAM is standard today, but has problems

- Advantages

- Capacity: Gb's

- Size: Efficient: small, cheap to make Gb's

- Speed: Fast ~12ns

- Endurance: Can be used 10<sup>15</sup> times

- DRAM challenges:

- Power consumption is high

- Needs external circuits to work extra power

- Loses data on power loss/interruption

- Structures struggling to get smaller

- Battery back-up schemes expensive, clumsy

Memory in servers estimated to use as much power as City of San Francisco

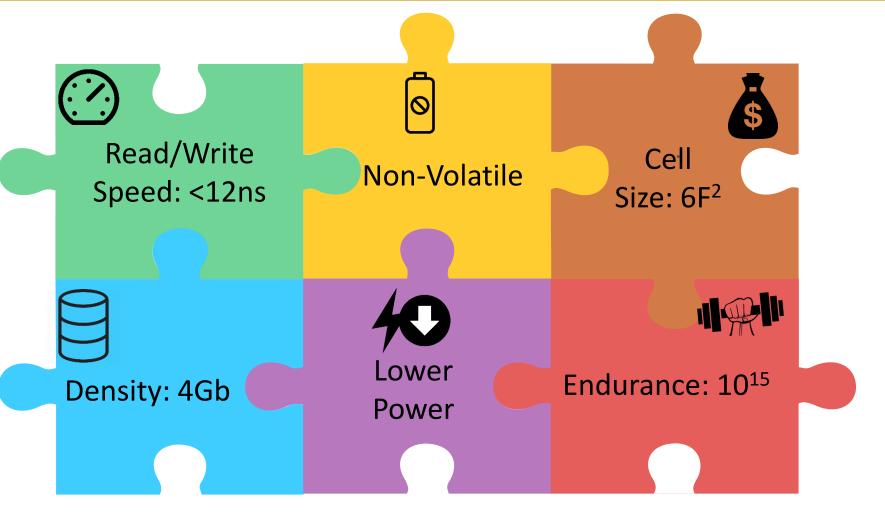

## MRAM has potential to disrupt memory market

#### Small (key to memory dominance)

- Can compete with DRAM sizes

- MRAM ½ to ¼ size of SRAM

- Lower Power (far superior to DRAM eg doubling smartphone life)

- Uses no power when idle

- Lower voltages

- No external circuity required

- Non-Volatile (key advantage over DRAM)

- Needs no power to remember

- Fastest "NV" in the world

- Fast (as fast as DRAM, even SRAM)

- <10ns switching speeds demonstrated</p>

- Can replace DRAM, SRAM

|                  | MRAM     | SRAM     | DRAM     | Flash    | FeRam   |

|------------------|----------|----------|----------|----------|---------|

| Read Speed       | Fast     | Fastest  | Medium   | Fast     | Fast    |

| Write Speed      | Fast     | Fastest  | Medium   | Slow     | Medium  |

| Array Efficiency | Med/High | High     | High     | Med/Low  | Medium  |

| Scalability      | Good     | Limited  | Limited  | Limited  | Limited |

| Cell Density     | Med/High | Low      | High     | Medium   | Medium  |

| Non-Volatility   | Yes      | No       | No       | Yes      | Yes     |

| Endurance        | SPIN     | Infinite | Infinite | Limited  | Limited |

| Cell Leakage     | Low      | Med/High | High     | Low      | Low     |

| Low Voltage      | Yes      | Yes      | Limited  | Limited  | Limited |

| Complexity       | Med/High | Low/Med  | Medium   | Med/High | Medium  |

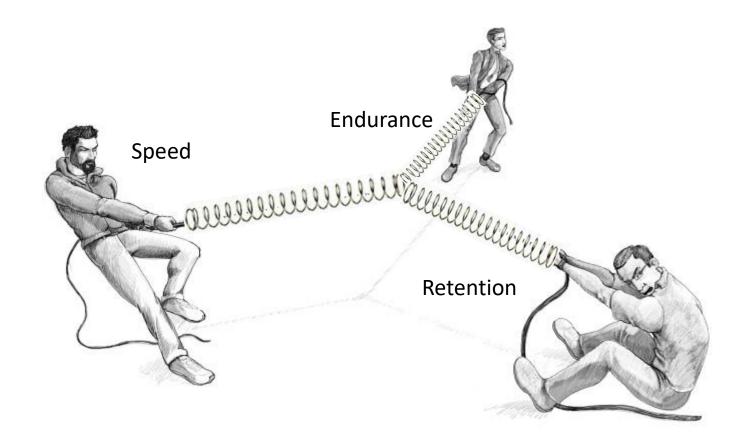

# So why hasn't MRAM disrupted already?

No one has solved the MRAM trade-off between endurance, speed and retention:

- Endurance <10<sup>10</sup>

- Speed >20ns

- Retention good

#### Plus:

- Writing is "probabilistic"

- Sub 30nm tolerances difficult

# What's required to replace DRAM?

- MRAM is inherently non-volatile and low power

- STT's MRAM already meets DRAM speeds

- STT's technologies have the potential to unlock the other specifications

# Design plan to unlock commercial grade MRAM

## Why are we so excited?

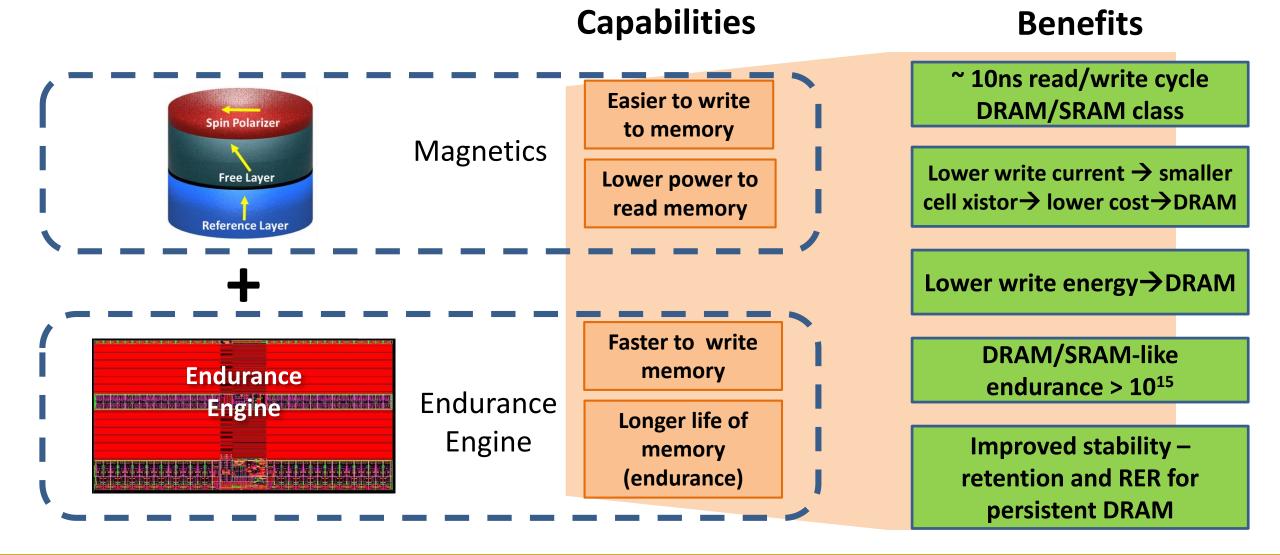

- World-beating magnetics: proprietary pMTJ/Spin Polarizer combination

- Provides material improvements to pMTJ efficiencies

- pMTJ must be very small to compete with DRAM

- As pMTJ shrinks, value of Spin Polarizer rises

- Deterministic write onset

- "Endurance Engine" is proprietary design IP with unique degrees of freedom

- Allows smaller write currents  $\rightarrow$  smaller cells

- Smaller cells  $\rightarrow$  lower cost

- Boost memory endurance by up to six orders of magnitude

- Universal  $\rightarrow$  potentially applicable to anyone's pMTJ

- Works on NVM, SRAM or DRAM

- Anticipate 100 patents by Q1 2018

#### STT: combining magnetics + circuits The path to persistent DRAM

## World class executive team

- **CEO: Tom Sparkman** 35 years experience in medical, semiconductor and wireless technologies, including GM Analog BU (Japan) and SVP WW Sales at Spansion, Inc. Integrated Fujitsu Micro acquisition and key member of Exec team that sold Spansion to Cypress; SVP WW Sales and GM Comms BU at IDT, Founding CEO at Samplify, Early Employee and 19 years at Maxim. Founding member of Maxim Europe, six years in Munich

- CTO, VP Magnetics Technology: Mustafa Pinarbasi, PhD 30+ years experience in thin film materials and magnetic thin film technologies, technology leadership positions at IBM, Hitachi Global Storage Technologies (HGST) and SoloPower, pioneered the development of GMR read sensor at IBM and TMR read head processing at HGST. Holds over 190 US patents

- **VP, Product: Andy Walker, PhD** is a 30+ years experience in the semiconductor industry, including with Philips Research Laboratories, Eindhoven, Cypress Semiconductor, Artisan Components and Matrix Semiconductor. He has been involved with 3-D Flash memory technology since 2000 and founded Schiltron Corporation to investigate and develop new 3-D Flash technologies. Holds over 40 US patents

- **VP Memory Integration, Patent Strategy: Amitay Levi, PhD** 30+ years experience in technology development of non-volatile memory, including Flash and MRAM. Developed technology from early start to high volume production in multiple foundries around the world

- **VP Business Development: Jeff Lewis** 30+ years semiconductor experience, including Senior VP of Business Development and Marketing at SuVolta, Inc. and at Innovative Silicon, and additional roles as CEO of CiraNova, VP positions at FormFactor, Artisan Components and Compass Design Automation

- **VP IC Product Development: Les Crudele** –40+ years semiconductor experience including VP & GM of Motorola's PowerPC RISC Division, VP & GM Compag's Workstation Products, and CEO of Banderacom, Transmeta and Azuray. Holds 10 patents

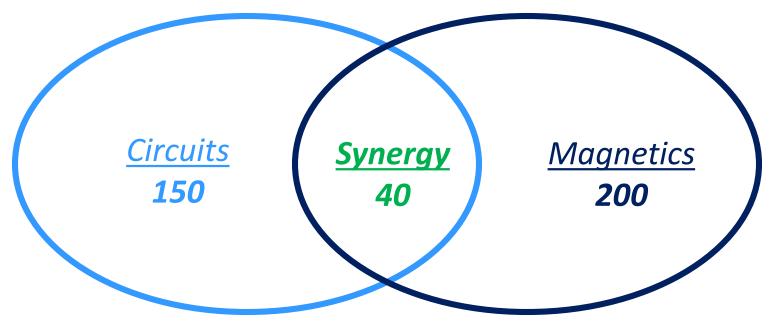

## 400 man-years' engineering; own fab

- World class team with 15 PhD's. Total team of 40

- 200+ years magnetics experience; 120+ years of memory design experience

- Complete in-house engineering and physics teams

- Physics

- Electrical engineering

- Thin-film engineering

- Mechanical engineering

- Test engineering

- Reliability engineering

- 3D memory design

## Next 6 months

- Q4 2017

- 1G of characterization data on pMTJ collected

- Competitive pMTJ

- Q1 2018

- Filed / granted 100 patents

- Emulator demo of Endurance Engine

- FPGA demo of Endurance Engine

- Confirmation of Spin Polarizer; 28nm pillar demo

# Medium term STT goals

- Deliver commercial grade ST-MRAM in 2019 that meets SRAM specifications

- Substantial progress against DRAM specifications through 2018

- Deliver DRAM-grade ST-MRAM with partner in 2020 targeting \$20 billion market segments

- Expect to generate revenue in 2018, with multiple revenue opportunities going forward through product and separate licensing of core technologies

## Summary

- MRAM has potential to replace embedded SRAM and key DRAM segments

- DRAM is \$20Bn market; limits of DRAM challenged, especially for enterprise and mobile

- MRAM has potential to disrupt SRAM and DRAM markets

- STT technology has potential to meet requirements for SRAM and DRAM replacement

- STT's differentiated technology and capabilities expected to enable meaningful performance advantages for its own and third party structures, in time for emerging market

- Three core elements:

- Smaller, faster pMTJ structures

- Patented/Pending Spin Polarizer

- Patented/Pending Endurance Engine

- Fast turn, world-class Fabrication plant

- Multi-disciplined, synergistic engineering team

- \$22.8M bridge to Series B (Q1 2018) will fund achievement of material milestones and provide path to bringing in strategic investors

## Glossary

- **MRAM** Magnetic Random Access Memory. MRAM requires no power to retain data.

- **MTJ** Magnetic Tunnel Junction

- **pMTJ** Perpendicular Magnetic Tunnel Junction

- SRAM Static Random Access Memory. SRAM requires power to retain data.

- **DRAM** Dynamic Random Access Memory. DRAM requires power to retain data.

- Non-Volatile Memory (NVM) Retains its data with power off

- Volatile Memory Loses data with power off

- **1T1J** Memory cell with 1 Transistor and 1 MTJ

- Persistence Ability of a memory to retain data without power for a limited time

- Endurance Number of write/erase cycles before memory becomes unusable

- **Retention** Capability of memory to retain state without power after cycling and at higher temperature