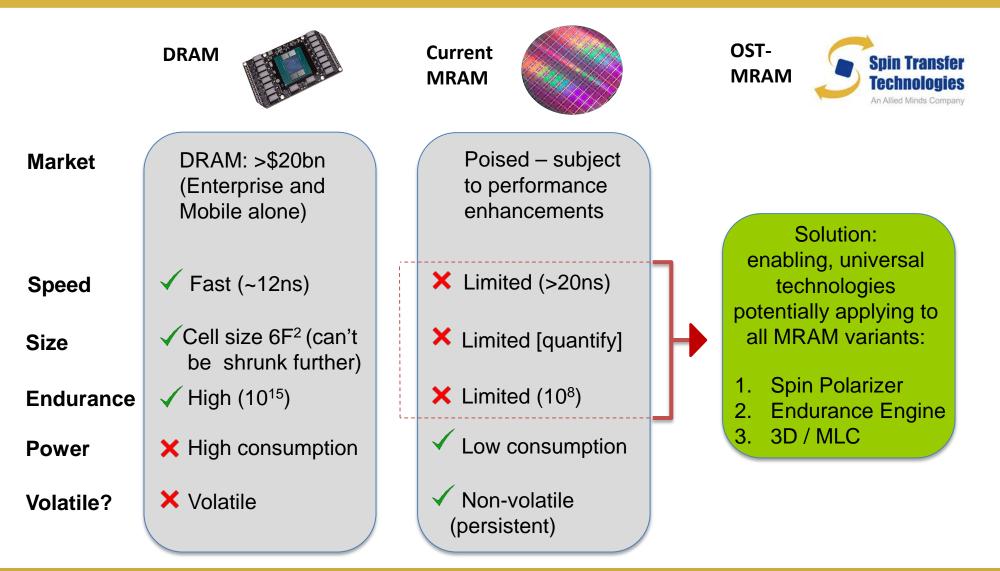

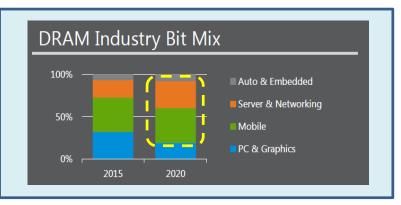

Universal technologies enabling DRAM-grade MRAM Unlocking the >\$20bn+ DRAM market (Mobile & Enterprise) Powering the next generation of applications

#### Disclaimer

The following presentation, including any printed or electronic copy of these slides, the talks given by the presenters, the information communicated during any delivery of the presentation and any question and answer session and any document or material distributed at or in connection with the presentation (together, the "Presentation"), has been prepared by the Company. The information in the Presentation is not intended to form the basis of any contract. By attending (whether in person or by telephone) or reading the Presentation, you agree to the conditions set out below.

THIS PRESENTATION IS NOT A PROSPECTUS. The Presentation does not constitute or form part of any offer or invitation to sell or issue, or any solicitation of any offer to purchase or subscribe for, any shares or other securities of the Company, nor shall it (or any part of it), or the fact of its distribution, form the basis of, or be relied on in connection with or act as any inducement to enter into, any contract whatsoever relating to any securities.

The Presentation is provided for general information only and does not purport to contain all the information that may be required to evaluate the Company. The information in the Presentation is provided as at the date of the Presentation (unless stated otherwise) and is subject to updating, completion, revision and further verification. No reliance may be placed for any purpose whatsoever on the information or opinions contained or expressed in the Presentation or on the accuracy, completeness or fairness of such information and opinions. To the extent permitted by law or regulation, no undertaking, representation or warranty or other assurance, express or implied, is made or given by or on behalf of the Company, or any of its parent or subsidiary undertakings or the subsidiary undertakings of any such parent undertakings or any of their respective directors, officers, partners, employees, agents, affiliates, representatives or advisors, or any other person, as to the accuracy, completeness or fairness of the information or opinions contained in the Presentation. Save in the case of fraud, no responsibility or liability is accepted by any such person for any errors, omissions or inaccuracies in such information or opinions or for any loss, cost or damage suffered or incurred, however arising, directly or indirectly, from any use of, as a result of the reliance on, or otherwise in connection with, the Presentation. In addition, no duty of care or otherwise is owed by any such person to recipients of the Presentation.

Nothing in the Presentation is, or should be relied on as, a promise or representation as to the future. The Presentation includes certain statements, estimates, opinions and projections provided by the Company in relation to strategies, plans, intentions, expectations, objectives and anticipated future performance of the Company and its subsidiaries. By their nature, such statements, estimates, opinions and projections involve risk and uncertainty since they are based on various assumptions made by the Company concerning anticipated results which may or may not prove to be correct and because they may relate to events and depend on circumstances that may or may not occur in the future and may be beyond the Company's ability to control or predict. No representations or warranties of any kind are made by any person as to the accuracy of such statements, estimates, opinions or projections, or that any of the events expressed or implied in any such statements, estimates or projections following the date of this Presentation. No statement in the Presentation is intended as a profit forecast or a profit estimate.

Certain industry and market data contained in this Presentation has come from third party sources. Third party industry publications, studies and surveys generally state that the data contained therein have been obtained from sources believed to be reliable, but that there is no guarantee of the accuracy or completeness of such data. While the Company believes that each of these publications, studies and surveys has been prepared by a reputable source, the Company has not independently verified the data contained therein. In addition, certain of the industry and market data contained in this Presentation comes from the Company's own internal research and estimates based on the knowledge and experience of the Company's management in the market in which the Company operates. While the Company believes that such research and estimates are reasonable and reliable, they, and their underlying methodology and assumptions, have not been verified by any independent source for accuracy or completeness and are subject to change without notice.

By accepting receipt of, attending any delivery of, or electronically accessing, the Presentation, you acknowledge and agree to be bound by the above limitations and conditions.

## STT: DRAM-grade MRAM

Universal, enabling technologies unlocking a \$20bn+ market

STT's 3 patented, universal technologies Potential to solve MRAM's endurance, size and speed limitations

#### Endurance Engine pPMTJ + Spin Polarizer (circuitry) (magnetics)

Spin Polarizer Free Layer Reference Layer 3-D/MLC (synergy)

- Up to 10<sup>6</sup> endurance boost

- Potentially compatible with any MTJ

- Increases yields

- 30-40 patents\*

- Parallels to SanDisk

\* Patents + Patent Pending

- Up to 30% efficiency increase

- Shrinks array size

- Speeds switching

- 30-40 patents\*

- From NYU Initially

- "MLC" MRAM

- 3-D MRAM

- Smaller geometries

- Testing/reliability

- Synergy

- 30-40 Patents\*

#### Enhancing MRAM performance Addressing IoT, mobile and Enterprise segments

|              | ΙοΤ                  |                 |                      | Mobile Computing |                 |                      | Data Centers/LPDRAM |                 |                      |

|--------------|----------------------|-----------------|----------------------|------------------|-----------------|----------------------|---------------------|-----------------|----------------------|

|              | Execute-<br>in-Place | Current<br>MRAM | Spin's<br>Technology | eSRAM<br>(cache) | Current<br>MRAM | Spin's<br>Technology | DRAM &<br>LP-DRAM   | Current<br>MRAM | Spin's<br>Technology |

| Endurance    |                      | ×               |                      | Ø                | ×               |                      |                     | ×               | ☑                    |

| Speed        |                      | ×               |                      |                  | ×               |                      |                     | x               |                      |

| Size         | ×                    |                 |                      | ×                |                 |                      |                     | x               |                      |

| Non volatile | x                    |                 |                      | ×                |                 |                      | x                   |                 |                      |

| Power        | ×                    |                 |                      | ×                |                 |                      | ×                   |                 |                      |

|              | TAM: Emerging        |                 |                      | TAM \$500M       |                 |                      | TAM \$20B+          |                 |                      |

STT targeting enhancements that unlock critical performance gains

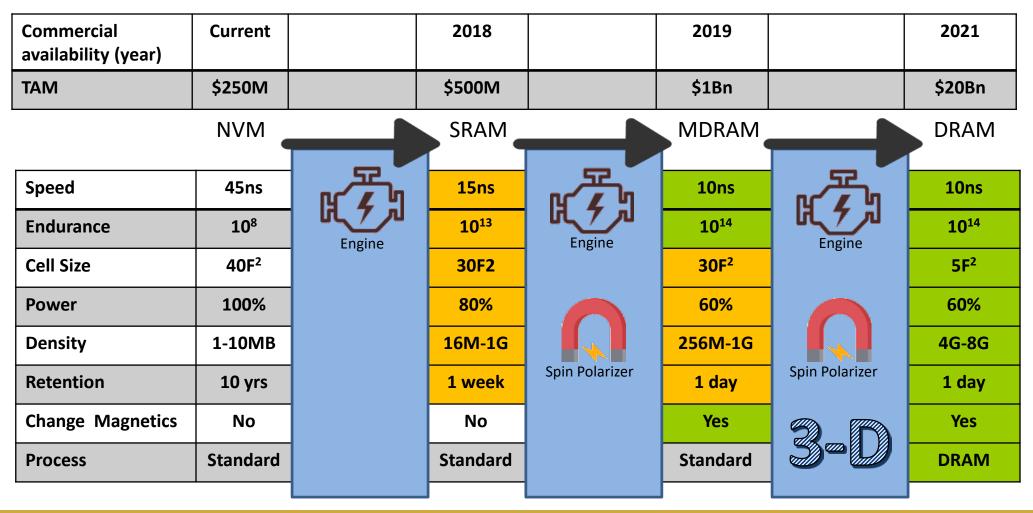

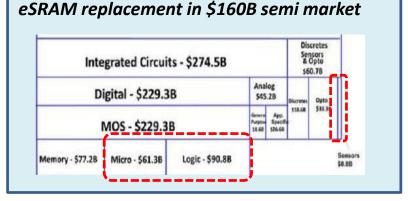

#### Market opportunity exceeds \$20bn Starting with SRAM in 2019; DRAM 2021

#### Step One: SRAM-Replacement - 2019

- Prove technology quickly by leveraging existing solutions at foundries

- Stand-alone/embedded SRAM Replacement

- Licensed to foundries/IDMs/partners

- \$500m TAM

- Critical component of ~\$80B semi market

- Step Two: Persistent DRAM 2021

- Holy Grail of memory opportunities

- Revolution in computer architectures

- Key to IoT, AI, HPC, Mobile, etc. advances

- Product ~\$20B+ TAM

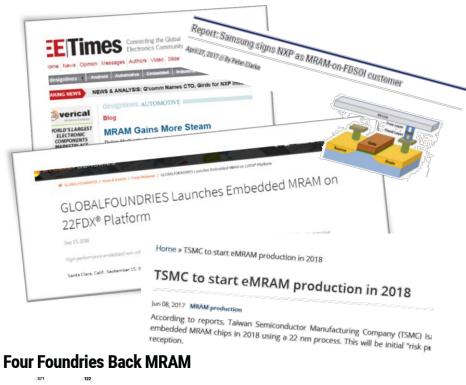

#### MRAM: the EMERGED next-gen memory Market for STT's MRAM enabling solutions already exists

3 foundries shipping MRAM next year as NVM (flash) replacement

- TSMC Multiple nodes; advanced nodes

- Samsung NXP/Qualcomm Partner

- GlobalFoundries Everspin Partner

All other foundries beginning MRAM

Potential market for all of STTs' offerings

Extensive work at other companies, e.g.

- SK Hynix + Toshiba DRAM replacement

- Intel–NVM Memory

- Qualcomm Cache memories

#### MRAM EcoSystem Exists

- Magnetics is a solvable problem

- Advanced Tools Exist. TEL Leads the pack.

- Materials, Know-How

Next-gen embedded memory technology ramps up in wake of flash scaling issues.

AUGUST 23RD, 2017 - BY: MARK LAPEDUS (HTTPs://SEMIENGINEERING.COM/AUTHOR/MARK-LAPEDUS/)

á

Four major foundries plan to offer MRAM as an embedded memory solution by this year or next, setting the stage for what finally could prove to be a game-changer for this next-generation memory technology.

GlobalFoundries, Samsung, TSMC and UMC plan to start offering spin-transfer torque magnetoresistive RAM (ST-MRAM or STT-MRAM) as an alternative or a replacement to NOR flash, possibly starting later this year. This represents a big shift in the market, because

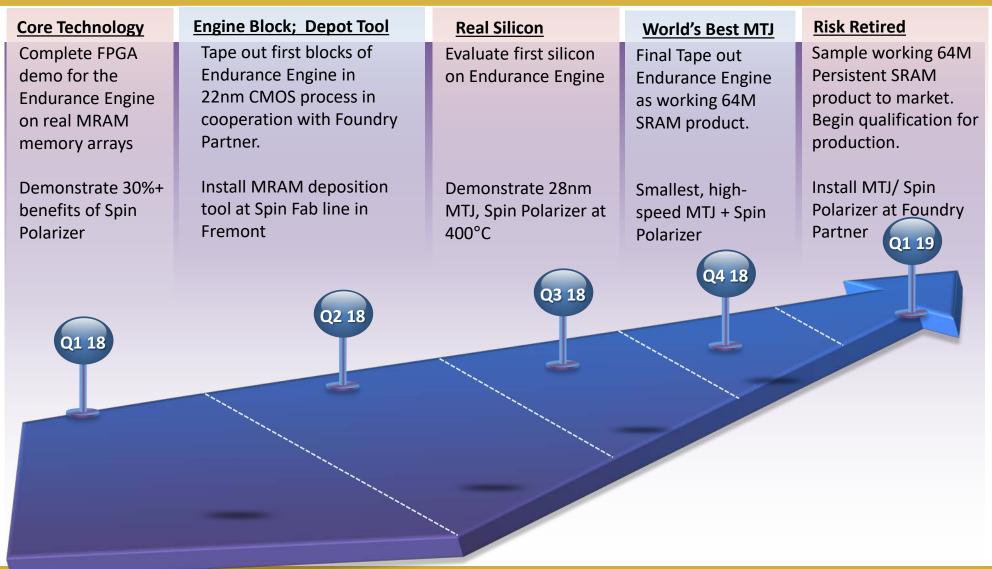

#### Proving performance claims in the lab Potential for substantial technology risk retirement by H1 2019

- System Beneficiaries

- Technology leaders would be key partners, technology drivers

- Non-volatile memory holds potential to revolutionize their architectures, with radical advances in compute power and reductions in power consumption

- Apple, Google, Amazon, Arm, Qualcomm, Huawei, Tencent, Alibaba, Fujitsu, etc

- Memory and Semi Companies

- Medium-sized memory (Cypress, ISSI, Giga, etc.) MRAM potential key to strategies

- Larger DRAM companies (Samsung, Hynix, Micron, etc.) want cost, density. STT potentially has all the pieces

- MCU Companies want <28nm embedded memory solution. Intel, ST, Microchip, Renesas, Avago, etc

- SoC Companies want <28nm SRAM solution. Apple, Samsung, Qualcomm, Avago, etc

- Foundries (TSMC, SMIC, UMC)

- No solution for Flash and SRAM below 28nm. This is a major issue for the entire industry

- All must have MRAM technology

- MRAM must be "easy." Engine does that. We can potentially sell to all of them, even competitors

- China, Inc.

- Tremendous amount of wafer capacity being built now. What will they use it for?

- China, Inc. has limited access to DRAM. No access to 3D NAND. MRAM the only path?

- Memory arguably is the only thing big enough to fill these huge fabs

### How has "little old" STT achieved this?

#### Time/IP

- STT founded in 2006 on spin polarizer technology sourced from NYU we've been at it a long time!

- S

- \$121m invested to date

- Delivering a proprietary Fab far superior cycle times

- World class mag

- World class magnetics and circuitry teams 22 PhDs

- Synergistic collaboration between the two

- Purist focus on scientific R&D in early years (now commercially targeted)

- - Holistic, system based approach, focusing on the end-user view

Partnerships

- TEL: leading producer of MRAM manufacturing tools globally

- STT/TEL collaborative engineering agreement gives STT early access to TEL equipment and engineering resource, further accelerating cycle times beyond peers'

# Unlocking a premium exit valuation

| Disruptive innovation<br>solving an important<br>problem | <ul> <li>Inherently non-volatile + lower power consumption</li> <li>Particularly suited to fastest growing Mobile and Enterprise segments         <ul> <li>low power consumption critical</li> </ul> </li> <li>Advances in DRAM are capped out by physics</li> </ul> |  |  |  |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Favourable market<br>dynamics                            | <ul> <li>Mobile and Enterprise DRAM segments: &gt;\$20bn; growing fast</li> <li>2018 the "year of MRAM"</li> <li>Semiconductor stocks at record highs. Lots of cash</li> </ul>                                                                                       |  |  |  |

| Sustainable competitive advantage                        | <ul> <li>&gt;100 patents in place covering 3 key technologies</li> <li>R&amp;D Fab and TEL agreement: superior cycle times</li> </ul>                                                                                                                                |  |  |  |

| Route to widespread adoption                             | <ul> <li>Scope for licensing model</li> <li>Separate technologies can be licensed by field of use</li> </ul>                                                                                                                                                         |  |  |  |

| Capable management, with aligned interests               | <ul> <li>Semiconductor veterans</li> <li>Right blend of commercial and scientific experience</li> </ul>                                                                                                                                                              |  |  |  |

| Establish potential for competitive tension              | <ul> <li>DRAM incumbents need an MRAM solution</li> <li>We believe that only STT's technology can unlock DRAM-grade MRAM</li> </ul>                                                                                                                                  |  |  |  |

#### Come see for yourself! 45500 Northport Loop West, Fremont CA 94538

#### **Reference materials**

## World Class ExecutiveTeam

- CEO: Tom Sparkman 35 years experience in medical, semiconductor and wireless technologies, including GM Analog BU (Japan) and SVP WW Sales at Spansion, Inc. Integrated Fujitsu Micro acquisition and key member of Exec team that sold Spansion to Cypress; SVP WW Sales and GM Comms BU at IDT, Founding CEO at Samplify, Early Employee and 19 years at Maxim. Founding member of Maxim Europe, six years in Munich.

- CTO, VP Magnetics Technology: Mustafa Pinarbasi, PhD 30+ years experience in thin film materials and magnetic thin film technologies, technology leadership positions at IBM, Hitachi Global Storage Technologies (HGST) and SoloPower, pioneered the development of GMR read sensor at IBM and TMR read head processing at HGST. Holds over 190 US patents.

- VP, Product: Andy Walker, PhD –is a 30-year-plus veteran of the semiconductor industry. He was with Philips Research Laboratories, Eindhoven, Cypress Semiconductor, Artisan Components and Matrix Semiconductor. He has been involved with 3-D Flash memory technology since 2000 and founded Schiltron Corporation to investigate and develop new 3-D Flash technologies. He has over 40 US patents to his name.

- VP Memory Integration, Patent Strategy: Amitay Levi, PhD more than 30 years experience in technology development of non-volatile memory, including Flash and MRAM. Developed technology from early start to high volume production in multiple foundries around the world.

- VP Business Development: Jeff Lewis 30+ years semiconductor experience, including Senior VP of Business Development and Marketing at SuVolta, Inc., the same role at Innovative Silicon, and additional roles as CEO of CiraNova, and VP positions at FormFactor, Artisan Components and Compass Design Automation.

- VP IC Product Development: Les Crudele –40+ years semiconductor experience including executive and technical leadership roles, including VP & GM of Motorola's PowerPC RISC Division, VP &GM of Compaq's Workstation Products, and CEO of Banderacom, Transmeta and Azuray. Holds 10 patents.

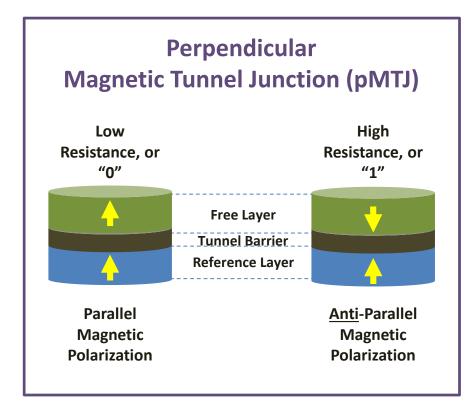

### What is ST-MRAM?

- MRAM is <u>Magneto-resistive RAM</u>

Magnetic polarization sets '1', '0'

- STT is <u>Spin Transfer Torque</u>

- Electron spin sets Free Layer polarization

- ST-MRAM using pMTJ is latest MRAM generation

- Bitcell uses 1 transistor + 1 MTJ

- Very dense configuration

- Attributes:

- Non-volatile

- High-speed read and write

- High endurance

- Easy integration in BEOL no impact on FEOL

#### Glossary

- **MRAM** Magnetic Random Access Memory. MRAM requires no power to retain data.

- **MTJ** Magnetic Tunnel Junction

- **pMTJ** Perpendicular Magnetic Tunnel Junction

- **SRAM** Static Random Access Memory. SRAM requires power to retain data.

- **DRAM** Dynamic Random Access Memory. DRAM requires power to retain data.

- Non-Volatile Memory (NVM) Retains its data with power off

- Volatile Memory Loses data with power off

- **1T1J** Memory cell with 1 Transistor and 1 MTJ

- **Persistence** Ability of a memory to retain data without power for a limited time

- Endurance Number of write/erase cycles before memory becomes unusable

- **Retention** Capability of memory to retain state without power after cycling and at higher temperature